AI加速引擎(AI加速器生态系统)

今天的设计团队如果采用传统的 RTL 设计流程,将花费很多时间才能将运算密集型网络带入到硬件中,该领域亟需一个有别于以往 RTL 流程,同时又能有效提高生产力的方法。

CATAPULT HLS 平台的时代来临

15 年前,Mentor 认识到设计和验证团队需要从 RTL 升级到 HLS 层级,并开发 Catapult®HLS 平台。该平台提供了从 C 到最佳化 RTL 的完整流程(图 1)。

图 1:Catapult HLS 平台

Catapult HLS 平台为算法设计师提供硬件设计解决方案,可以从 C /SystemC 描述,生成高品质的 RTL,并且以 ASIC、FPGA 或 eFPGA 为目标。此平台能在合成之前检查设计中的错误、为功能验证和覆盖率分析提供无缝且可重复使用的测试环境,同时支持在生成的 RTL 与原始 HLS 来源之间执行形式等效性检查。

该解决方案的优势包括:

- 支持后期阶段变更。可随时变更 C 算法,重新生成 RTL 代码或使用新制程。

- 支持硬件评价。可迅速地探索功耗、性能和面积选项,而无需变更原始代码。

- 加快时程。将设计和验证所花时间从一年缩短至几个月,可在数日内增添新功能,使用的 C/C 代码行数比 RTL 减少 5 倍。

AI 加速器生态系统

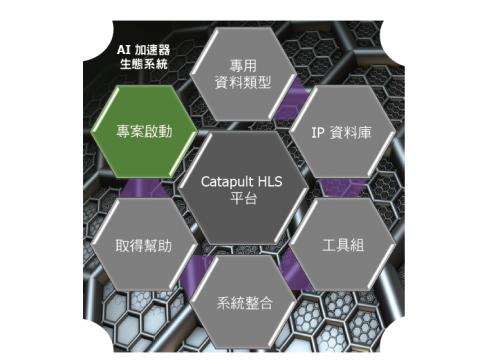

同时,Mentor 在 Catapult HLS 平台中部署了 AI 加速器生态系统(图 2),为 AI 设计师提供能快速展开项目的环境。

图 2:Catapult AI 加速器生态系统

AC MATH 数据库

Algorithmic C Math(AC Math)中的所有函数都以 C 模板参数写成,让设计师可依据目标应用来指定数值的精准度。许多函数都使用不同的近似策略,例如,自然对数提供两种形式,即分段线性近似和 cordic 形式。在可接受准确度稍有误差的情况下,前者较小且较快; 后者虽然较慢,但准确许多。所有情况下都能自定义来源以达成设计目标。每个功能/内存块都附有详细的设计文件和 C 验证程序。由于 Catapult HLS 平台会利用 C 验证程序,因此很容易根据来源设计来验证 RTL 准确度。

该数据库中的数学函数类别包括:

- 分段线性函数 - 绝对值、正规化、倒数、对数和指数(自然和底数 2)、平方根、反平方根和正弦/余弦/正切(正和反)

- 激励函数,如双曲正切、S 函数和 Leaky ReLU 函数

- 线性代数函数,如矩阵乘法和 Cholesky 分解

DSP 数据库

Algorithmic C DSP(AC DSP)数据库定义了 DSP 设计师通常所需要的可合成 C 函数,例如滤波器和 FFT。这些函数采用以 C 类别为主的设计,让设计师能轻松示例物件的众多变体,以打造复杂的 DSP 子系统。与 AC Math 数据库一样,输入和输出参数都会参数化,以便能在所需的定点精确度下执行算术,从而在为合成的硬件执行面积和性能折衷时,提供高度的弹性。

DSP 数据库包含:

- 滤波器函数,如 FIR、1-D 移动均值,以及多相位抽取

- 快速傅立叶变换(FFT)函数,如 radix-22 单一延迟回授、radix-2x 动态就位和 radix-2 就位图像处理数据库 Algorithmic C 图像处理数据库(AC IPL)首先会定义一些常见的像素格式类型定义。

AI 加速器生态系统还可提供丰富的工具组,由真实且经过测试的加速器参考设计示例,团队可以研究、修改和复制这些示例,迅速展开项目。这些随 Catapult 提供的套件,包含了可设定的 C /SystemC IP 原始代码、文件纪录、验证程序和指令码,让设计能进行 HLS 合成和验证流程。这些工具组展示了各种能用来对性能(延迟)、帧率、面积或功率的折衷进行实验的方法和编写程序技术。

PIXEL-PIPE 视讯处理工具组

该视讯处理工具组展示了一个使用 pixel-pipe 加速器的即时图像处理应用程序(图 3)。加速器内存块使用 C 类阶层构架来实作。该内存块将图像缩小,并将图像从彩色转换为单色,以执行边缘侦测,然后放大图像。Xilinx®PetaLinux 下的 CPU 上,执行了一个使用者空间应用程序,此程序能让软件控制开启或关闭边缘侦测内存块。工具组文件纪录会显示如何使用 Xilinx IP 将该内存块整合到 Xilinx 电路板中,以便团队展示该系统。

图 3:Pixel-pipe 视讯处理工具组

2-D 折积工具组

该工具组展示了如何以 C 对 Eyeriss1 处理元件(PE)数组进行编码,实作 2-D 折积以执行图像的强化(锐化、模糊和边缘侦测)。处理元件(图 4)可以执行 3x1 乘积累加(折积)。

图 4:Eyeriss 处理元件

TINYYOLO 物件辨识工具组

物件辨识工具组(图 5)展示了使用折积加速器引擎的物件辨识应用程序,该引擎使用 2-D Eyeriss 工具组中的 PE 数组实现。该工具组展示了如何透过 AXI4 互连(从系统內存来读取核心权重数据)取得高速数据路由,并展示如何定义高效能內存构架。该工具组提供 TensorFlow 整合能力,可以 C 语言的网络层能进行推理测试。

图 5:TINYYOLO 工具组示例 - 系统视图

系统整合

加速器内存块并非独立存在,Catapult HLS 提供“界面合成”能力,以将时间性协定加入至非时间性 C 函数界面变数。设计师只需要在 Catapult GUI 中,为协定设定构架约束条件。此工具可支持典型的协定,例如 AXI4 视讯串流、请求/认可交握,以及內存界面。这让设计师不必变更 C 原始码,就能探索界面协定。

AXI 示例

AXI 示例(图 6)显示了如何使用 Catapult HLS 产生的 AXI 界面 IP,在 AXI SoC 子系统中示例一个或多个加速器元件。提供主控端、受控端和串流示例。

图 6:AXI 示例

基础处理器示例

基础处理器示例(图 7)显示了如何将机器学习加速器连接到完整的处理器型系统中,并采用了 AXI 示例。此示例中的机器学习加速器采用了简单的乘积/累加构架,搭配 2-D 折积和区域取最大值。支持数个第三方处理器 IP 模型,并包含一个用于裸金属编程的软件流程(含有相关数据)。

图 7:基础处理器平台示例

,免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com