eda行业报告(工业软件专题报告)

(报告出品方/作者:华创证券)

一、EDA 行业简介EDA(Electronic Design Automation)是指利用计算机软件完成集成电路的设计、仿真、验证等流程的设计方式。EDA 工具作为集成电路领域的基础工具, 广泛应用于集成电路设计、制造、封装和测试等环节,实现电路设计、版图设计、版图验证、性能分析等工作的计算机自动处理。

(一)EDA 行业根植在集成电路产业之上

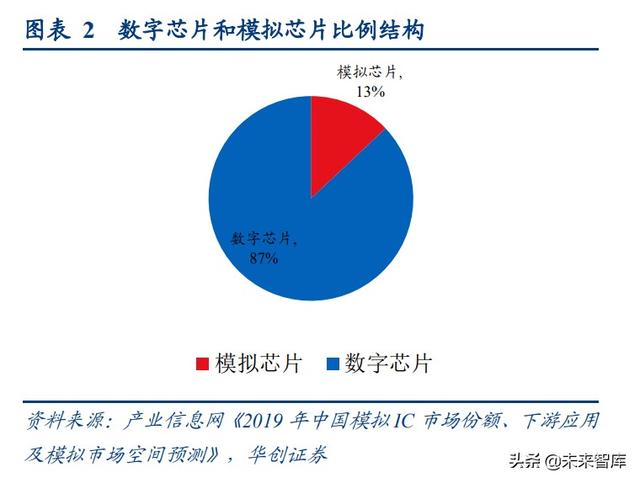

集成电路市场规模大,数字芯片为主流:随着消费电子产品市场渗透率不断提高,集成电路行业市场日趋成熟,尤其在近年来以 5G、物联网、人工智能等新兴应用场景的推动下,全球集成电路市场规模平稳增长。

集成电路可以大致分为数字芯片和模拟芯片:数字电路集成电路是处理数字信号的器件;而模拟集成电路是处理和提供模拟信号的器件。

EDA 行业市场规模稳定增长,我国 EDA 市场仍有较大空间。EDA 行业与集成电路行业 息息相关,随着集成电路市场规模的扩大 EDA 行业市场规模稳步上升。我国 EDA 行业 发展滞后,按照 2020 年全球 EDA 市场规模相对于集成电路市场规模的比例测算,对应于我国集成电路市场的 EDA 行业规模应为 158 亿元,实际上仅为 66 亿元。

国内 EDA 市场规模偏小的主要原因有:

1) EDA 产值和集成电路设计工作相关,国内设计产值占比可能偏低;

2) 国内软件行业整体的正版化率不足,也会导致产值不及预期;

中国 EDA 市场有两大向上动力:

1) 随着中国国产半导体行业的成长,国内设计产值,设计公司,设计人员预计均将有较 大幅度的提升,市场天花板打开;

2) 国内软件正版化,包括监管环境的改善也能提升国内 EDA 的购买金额;

(二)行业竞争格局稳定,美国三巨头垄断全球市场份额

EDA 行业格局稳定,市场集中度较高:行业内部公司分为三梯队,第一梯队的 Synopsys、 Cadence 和 Siemens EDA 拥有较完整的全流程产品,垄断了全球超过 70%的市场份额, 收入规模及产品完整度远超后两梯队的企业。

三家公司各自在其擅长的领域不断深耕:正是由于三家公司针对芯片设计流程的不同环 节各有优势,使得 EDA 行业格局长期保持“三足鼎立”的稳定局面。

Synopsys(新思科技):拥有最全面的产品线,优势产品在于数字芯片设计、逻辑 综合等相关工具,如公司的逻辑综合工具 Design Compiler、静态时序分析工具 Prime Time、调试工具 verdi 等。

Cadence(楷登电子):由 SDA Systems 和 ECAD 两家公司合并而来,EDA 行业中 位居第二,优势产品在于模拟芯片设计相关工具。

Mentor Graphics:2017 年被西门子收购,优势产品在于 DFT 和 PCB 设计等环节, 如公司的 Calibre Signoff 和 DFT 等产品。

国内市场由第一梯队三家企业占据主导地位:2020 年国内 EDA 市场销售额中 80%归属 三巨头,本土企业中,华大九天占国内 EDA 市场份额的 6%,成为国内第四大 EDA 工具 企业。

国内 EDA 公司在部分环节有所突破,但尚未形成全流程产品覆盖:目前国内 EDA 企业 数量约 30 家,成立时间多在 2010 年之后,提供的 EDA 工具以点工具为主,其中不乏一 些已经具备竞争优势的产品。

(三)EDA 行业子领域众多,产品链条长

EDA工具的市场不是一个统一的市场,而是由芯片设计中众多环节所需的功能组合而来。 不同环节完成相应的算法,需要特定功能的软件工具,所有工具组合起来形成一套 EDA 工具体系。因此所谓的 EDA 大市场,实质上由数个功能软件小市场组成。

1、数字集成电路设计流程

数字芯片设计通常使用硬件描述语言或高级建模语言来描述电路逻辑,逻辑综合后将硬件语言转化为门级的网表,经过进一步验证和布局布线后,进行物理版图验证,产生 GDSII 文件用于工业制造。

2、模拟集成电路设计流程

模拟集成电路设计涉及到复杂的信号环境,需要大量人工干预决定取舍,且集成度相对较低,其设计的自动化程度要低于数字集成电路。设计者定义功能后进行算法的验证, 对电路应用仿真模拟进行验证,一旦通过验证即进行电路的版图设计,版图经过物理验 证后再次进行仿真模拟和验证后就可进入制造阶段。

二、EDA 行业竞争的三要素:可靠性、速度和生态(一)可靠性:芯片全流程巨大的 NRE 成本决定了可靠性是核心竞争力

EDA 工具的可靠性指的是使用 EDA 工具本身是否准确,是否能保证 BUG 风险点全覆盖, 若 EDA 工具本身包含一定的 BUG,最终可能造成设计结果就是错误的。

直接损失:随着芯片制程技术发展,从设计到流片的开发成本快速增长,下图展示了随 着芯片的一次性开发成本,一直随着工艺的进步指数级增长,28nm 时的一次成本已经达 到 160 万美元,据称 7nm 的一次性成本可能高达数千万美元。如果一次试验流片失败, 那么意味着这次试验的直接成本很大程度上完全损失,直接损失成本已经是一个天文数 字,甚至可能造成一些小公司濒临破产。

间接损失:由于流片的成本昂贵,芯片开发周期长,间接损失将比直接损失更多,更复 杂,主要的间接损失有:1)工期延误造成的团队人力损失;2)晚进入市场损失。

以三家代表性的 Fabless 公司在 2020 年研发支出的情况进行测算,若由于 EDA 工具的问 题,导致设计周期延长 3 个月(一次流片失败典型需要排查问题的时间),对于模拟芯 片设计,百人团队损失的成本约为 1500 万元~2000 万元;对于数字芯片设计,三百人团 队损失的成本约为 5000 万元~6000 万元。

更重要的损失是工期延误造成晚进入市场的损失,这可能造成的结果是丢失份额,甚至直接丢失客户,这样的损失虽然较难估算,但毫无疑问是客户无法承担的。

因此,所有 EDA 公司的核心竞争力,都是能够让客户信服自己的产品是稳定可靠的,不 会因为软件本身的算法缺陷或其他 BUG 造成流片失败。小公司对 EDA 造成失败损失承受能力更差,因此小公司在必须正版的约束下更愿意为海外 EDA 巨头 支付高昂的软件成本。

而对于大公司,其对可靠性愿意支付更高的成本且自身人力资源充沛,近年兴起在部分 工序采取两套工具链并行推进交叉验证的做法,主力团队用 A 厂商的工具链完成全套开发工作,同时一小部分人用 B 厂商工具链在部分工序交叉验证,力保部分高危工序不出错。这一最新流行的开发理念不仅扩大的 EDA 市场的总需求,也给了国产厂商可以突破的机会。

(二)速度:减少芯片设计时间,降低 Fabless 公司研发人力成本

芯片设计的 Fabless 公司的主要成本项是人,而人员的工作效率,也是由软件和工具直接决定的。提效性的衡量因素主要为 EDA 工具的计算速度和操作便捷度,计算速度越快, 越易于操作,工具的提效程度越高。最终节约的是公司整体人力成本:

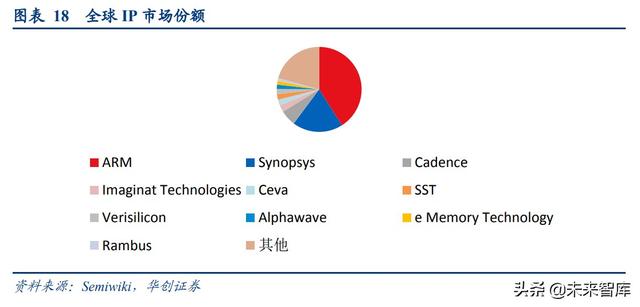

1)IP 模块复用可以很大程度提升设计速度。在美国,EDA 厂商是提供 IP 资源的渠道之 一,IP 将芯片设计中常用的复杂功能设计为可修改参数的模块,从而避免重复劳动,大大减轻工程师的负担,Fabless 通过获得 IP 授权来缩短芯片设计时间。

2)操作便捷度来源于用户使用习惯,即更换新工具的潜在时间成本。工业软件具有特殊 用途,是对实际工程技术的模型化和代码化,用户一旦掌握了某项工具软件,则会长期使用,工具之间的转换有一定的学习时间成本。

3)软件本身的算法,包括对多核并行架构的优化,也能决定软件运行的速度,部分国内 厂商在数字 EDA 领域的突围思路就是用简化算法大幅度压缩工程计算时间。

(三)生态:完整工具链以及和 IDM 厂商的生态合作

EDA 供应商内部产品生态:EDA 工具众多,且不同环节的输入输出格式有所差别,客户往往会选择一家厂商提供自己需要的全部工具,并依靠 EDA 厂商的 FAE 提供服务解决流程流畅性。

EDA 三巨头通过并购方式完善产品生态。三家头部公司正是在不断并购中成长为行业巨 头,三十年间三家公司并购事件近 300 次。

EDA 公司高度依赖外部合作生态,在产业链合作中不断迭代产品。EDA 工具的更新迭代 依赖于产业链,Foundry 晶圆制造厂将自身工艺的相关参数开发为 PDK,每进行一次工艺的更新,就需要开发一套 PDK 交由 EDA 供应商开发新的软件版本。作为软件供应方, EDA 公司也需要对软件使用方 Fabless 的需求保持快速的响应。因此,EDA 供应商需要 与 Foundry 晶圆制造厂及 Fabless 设计商进行密切沟通合作。

三、国内 EDA 行业的现状及机会(一)国产 EDA 发展滞后,但已培养出有亮点的产品

国产 EDA 受到重视,已经初步具备发展国产 EDA 工具的环境。EDA 工具成为美国遏制我国芯片产业发展的一大武器,国内对于发展国产 EDA 的重视度提升。政策上,国家对芯片设计的流片补贴等力度加大,并牵引建立产学研合作生态,资本不断涌入相关企业。多重利好因素下,国内 EDA 行业获得快速发展, 国内 EDA 厂商数量和融资情况明显改善。

(二)华大九天为国产 EDA 龙头公司

公司目前为国内 EDA 绝对龙头。华大九天成立于 2009 年,是国内最早从事 EDA 工具研发的公司之一,经过十几年发展, 目前已经成为国内规模最大、产品线最完整,综合实力最强的国产 EDA 企业。

公司的商业模式为“授权 服务”模式,通过销售 EDA 产品获得授权费,并提供集成电 路设计和制造领域的相关技术服务,收取服务费。

公司的核心优势:公司具备国内覆盖流程最广的产品,产品实力得到业务认可。公司的 EDA 工具覆盖了模拟电路设计全流程 EDA 工具系统、数字电路设计 EDA 工具、平板显 示电路设计全流程 EDA 工具系统和晶圆制造 EDA 工具等,其中,模拟电路设计和平板 电路设计 EDA 的部分工具达到国际领先水平。

(三)国产 EDA 的潜在发展机遇

人工智能技术与 EDA 行业双向推动。一方面,人工智能的芯片和算法成为各行各业取得 进步的关键,对于人工智能芯片的需求推动 EDA 厂商创新工具功能,在新的需求下建立 新的合作生态;另一方面,将人工智能技术应用于 EDA 工具中,处理芯片设计中的数据 和计算,可以有效提高芯片设计效率,缩短芯片设计周期,降低 Fabless 公司的时间成本 和人力成本。

我国在新一代信息技术上的优势为在新起点上发展 EDA 创造条件。在以人工智能技术 为引领的科技变革中,中国与其他国家在相同起点上,且已经具备领先优势。借助于我 国在新技术上的优势,国内 EDA 供应商有望加快赶超步伐。

云计算与 EDA 工具结合成为降本提效的重要方法。随着芯片设计工艺的规模越来越大, 对于服务器的要求也在加大,在芯片设计流程的前期和中期,服务器资源可控,但到项目后期,针对全芯片的仿真和物理验证等阶段对于计算资源的消耗巨大。

对于大公司,采取的应对是让不同项目组错开使用巅峰,来提高计算资源的利用效 率,但实践上由于工期的不可控性,甚至可能会发生不同项目组同时达峰的情况, 这样会导致紧缺的计算资源让项目延期,进一步恶化工期增加成本;

对于小公司,如果追求以最快的速度推出产品,难免需要购买先进的大型计算系统, 而一次性高额 capex 对小公司现金流就显得更是雪上加霜。此时,云计算按需付费, 可灵活扩容计算资源池的特点就对小公司显得特别有吸引力。

EDA 上云对国产 EDA 公司是一个机会,当前国内云计算涉及到牌照,云数据安全等 一系列的要求。国产 EDA 公司做本土的 EDA 云能更快地推出产品并做好本地服务。

国产 EDA 生态环境向好发展。在市场需求、人才培养和产业链生态的共同支持下,国内 EDA 生态的建立初步具备较好土壤。

市场需求生态:我国是电子设备的生产和消费大国,芯片设计行业市场需求旺盛。

人才培养生态:在政策和资金支持下,我国 EDA 行业的流失人才逐渐回归国内 EDA 厂商,同时,国内产学研协作力度加大,公司与高校和科研院所联系紧密,有利于 国内人才的培养和输送。

产业链生态: 我国芯片设计公司数量众多,晶圆制造工艺不断提升,下游厂商的发 展为建立国产 EDA 协同生态创造良好的条件。

在 EDA 国产化的背景下,我国国内的 EDA 厂商具备较大的国产化空间。

四、风险提示国内 EDA 软件厂商发展不及预期;

行业竞争激烈,造成盈利问题。

(本文仅供参考,不代表我们的任何投资建议。如需使用相关信息,请参阅报告原文。)

精选报告来源:【未来智库官网】。

「链接」

,免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com