基于dsp芯片的自适应滤波(多核DSP间基于SRIO数据传输的设计与实现)

魏智伟

(重庆邮电大学,重庆400065)

:在使用Digital Signal Processor (DSP)芯片进行数字信号处理时,由于数据量大,线程较多,通常采用多片DSP协同处理。本文旨在研究DSP间数据和信息传输的实现,并以三片TI的 TMS320C6474芯片为例,基于SRIO协议,设计一种传输架构,实现了DSP间的数据传输。最终实现DSP间2.520 Gb/s的数据传输速率,为理论值的50.40%,但如果除去线程调度和DSP间同步所用时间,其SRIO接口的数据传输速率可达到3.886 Gb/s,为理论值的77.72%。该设计具有较大的通用性,对其他同类型的芯片间的数据传输设计具有极大的参考性。

:多核;DSP;SRIO;DSP间数据传输

:TP368.2文献标识码:ADOI: 10.19358/j.issn.1674-7720.2017.04.011

引用格式:魏智伟.多核DSP间基于SRIO数据传输的设计与实现[J].微型机与应用,2017,36(4):36-39.

0引言

伴随着DSP所需处理的数据量和开发的功能模块的增多,单片DSP运行的进程数增多,负载过大,系统越来越难以满足实时处理的要求。如果选择多片DSP协同运行,不仅可以减少单片DSP的负载,提高系统的处理性能和响应速度,从而达到实时处理的要求,还能进行更多功能模块的开发,对于数字信号处理系统来说定是有益的。但多片DSP进行协同运行时,DSP间需要设计完成数据交互的功能。本文依据Rapid IO协议的标准,结合TI的TMS320C6474芯片的特点,在Digital Signal Processor_Basic Input Output System(DSP_BIOS)的开发平台上,设计和实现了多核DSP间的数据传输。本文首先介绍了该设计所需的各个功能模块,然后阐述整体设计的流程和具体实现的方式,最后对DSP间数据传输性能进行了测试。

1DSP间通信所需功能模块简介

1.1Mailbox(邮箱)

基于DSP_BIOS的开发平台,TI提供了一个Mailbox(MBX)模块,开发者可以通过TI的用户接口函数来进行管理,使用该模块。Mailbox用来图1用Mailbox实现线程间通信实现DSP内部的同一个核内的不同进程(TSK)间的相互通信[1]。MBX_post用于发送端,MBX_pend用于接收端,其实现示例如图1所示。

1.2Semaphore(信号通信)

TI提供了一个Semaphore[2]模块,该模块可以用于管理对共享资源的访问。其访问模式有三种:直接模式,间接模式,综合模式。本文采用的是直接模式:读取寄存器DIRECT的值,如果DIRECT的值为1,则表明该共享资源可用,允许访问,并获得该信号量;反之如果DIRECT的值为0,则表明该共享资源正在被其他进程访问。当对共享资源操作完成后,需要对DIRECT写1,以释放对该资源使用的权利。

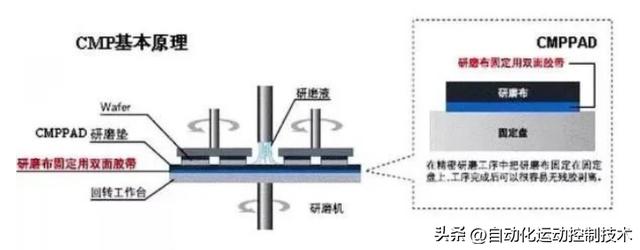

1.3Rapid IO

1.3.1Rapid IO简介

Rapid IO协议是一个开放的点对点分组交换标准,是面向嵌入式系统开发提出的高可靠、高性能、基于包交换的互联技术[3],传输速率能达到1 Gb/s以上。其最主要的特点包括:(1)有错误检测机制; (2)低负载高带宽;(3)引脚少[4]。

1.3.2Rapid IO架构

SRIO总线是一种开放式的基于包交换的高速串行标准总线[5],Rapid IO协议采用三层分级体系结构:

(1)逻辑层:规定了端点间传输的协议和包格式。

(2)传输层:定义了在系统中传输的包所需的路由信息。

(3)物理层:包含了硬件级接口的信息,比如电气特性、错误数据管理、基本数据流控制。

1.3.3SRIO包结构

在SRIO的包结构中,包的种类有很多,主要用到的为数据包和门铃包。数据包用于在源地址和目的地址间进行数据传输,其结构如图2所示。门铃包主要用于触发相应的中断,通知相应DSP的某个核进入中断响应函数,执行相应的操作,但门铃包不携带数据信息,其门铃包的结构如图3所示。

其中包结构各个段的含义是:AckID:交换结构期间将使用控制符号来确认是哪一个包;Prio:表明该包的优先级;tt:指定Device ID是用8 bit或16 bit表示;fftyp:表示包的类型;destID:包传送的目的地址ID;sourceID:发送包的源地址ID;CRC:包结构的校验保护;Info:门铃中断触发控制。

1.3.4Rapid IO包传输

包结构(packets)是SRIO传输两个端点之间传输的单位,其传输是基于请求包和响应包。图4发送端和接收端分包交互流程

其一次数据传输流程为:发送发起端产生一个请求包给接收端,接收端收到后返还一个响应包给发送发起端[6]。图4表明了发送端和接收端的包交互流程。

2DSP间通信的设计与实现

2.1资源的配置

2.1.1SRIO端口连接

每片TMS320C6474芯片有两个SRIO实体端口(分别命名为Port0,Port1),将其分别与另外两片DSP的任意一端口相连,如图5所示。通过该连接,可以保证任意一片DSP能与其他两片DSP直接连接。当发送端DSP和接收端DSP都已确定时,相应SRIO端口的选择也就确定了。

2.1.2DDR共享内存的分配与管理

每块DSP上都外挂一片DDR存储器。DSP的任意一个核Core0、Core1、Core2都能访问该存储器(TMS320C6474 为三核处理器,将三个核依次命名为Core0、Core1、Core2)。在DSP0,DSP1,DSP2的DDR存储器里指定一块内存用于存储DSP间任务调度的信息(以下称该段内存为共享调度内存),如图5所示。每片DSP上分配的公共调度内存的规划与管理如图6所示。对每个DSP三个核的内存分别分配一个Semaphore(信号通信)用于管理对接收端DSP的共享调度内存的访问。

2.1.3中断的分配与运用

当发送端将消息发送给接收端后,通知接收端相应的核来处理该消息。此次设计的方案是通过SRIO口传输门铃包(DOOEBELL Packet),门铃包携带接收端相应核的信息, 触发接收端相应核的中断。

当发送端发送DOORBELL包时,此包被用作初始化CPU中断,包结构中INFO段表明相关DOORBELL寄存器的相关中断位被设置,如图3所示。一个DSP有4个DOOEBELL寄存器,每个寄存器有16 bit,有64个中断源产生中断。通过ICR(Interrupt Condition Routing)寄存器,可以将每位路由给任意核。本文将DOORBELL寄存器的最低的三位分别分配给DSP的三个核(Core0,Core1,Core2)。即若DOOEBELL的最低位为1,则DSP的Coer0响应该中断。

每个DSP都有两个SRIO口,如图5所示,前面已经将DSP互连的SRIO口进行了编号(0,1),按照SRIO口的编号(0,1)分别分配以DOOEBELL 0和DOOEBELL 1寄存器,DOOEBELL 0和DOORBELL 1寄存器又分别映射到SRIO的两个中断通道(71~RapidIO Interrupt(2n),72~ RapidIO Interrupt(2n 1)),将此两个中断分别分配给两个SRIO口,使之分别响应SRIO口的中断。该Rapid IO Interrupt主要用于判断发送端的DSP的编号。如图7所示,接收端为DSP0,若中断通道71~RIOINT被触发,则判断发送端为DSP1,若中断通道72~RIOINT被触发,则判断发送端为DSP2。

通过以上中断的配置,可以保证发送端的任意DSP都能通过DOOEBELL消息包通知到消息接收端的任意核,同时接收端也能判断出发送端为哪个DSP。

2.2设计思路与具体实现

2.2.1设计思路

实现多核DSP间的数据交互主要完成两方面的工作:(1)实现数据的搬移;(2)通知接收端的DSP数据存储的位置和长度。其实现流程图如图8所示。

2.2.2具体实现流程

(1)SRIO初始化。①SRIO电源模块的初始化:对SRIO相关的模块提供电源。②SRIO的SERDES模块初始化:配置PLL,配置RX0、TX0和TX1、TX1的传输通道,配置SRIO的端口0和1。③检查SRIO口是否配置完成。

(2)选择SRIO端口。根据发送端的DSP和接收端的DSP决定选择SRIO口,即选择数据传输的物理链路。

(3)获取向接收端的共享调度内存写入消息的信号量。通过Semaphore(信号通信)管理不同发送端对接收端DSP的共享调度内存的访问,若该信号量被占用,则一直等待该信号被释放。

(4)通过SRIO口传输数据包。配置Load/Store Register完成消息包的组成。其关键配置有:配置LSUn_REG2中的DSP Address,完成待传输数据(payload)的源地址和目的地址的配置;配置LSUn_REG3中的Byte_count完成待传输数据的长度;配置LSUn_REG5中的Packet Type完成包种类的配置。配置完成后,使能传输。其Load/Store Register相应字段的配置会映射到数据包中,待传输数据通过SRIO口存到了公共调度内存中。

(5)通过SRIO口传输DOOEBELL包:该包用于通知接收端DSP的相应核的共享调度内存有消息待处理。通过对LSUn_REG5的Drbll Info段进行配置,使之映射到DOORBELLn_ICRR寄存器中,本文将DOOEBELLn_ICRR的第0位、第1位和第2位,通过ICR(Interrupt Condition Routing)寄存器使之分别路由到核0、核1、核2。则通过DOOEBELL包就能在接收端DSP相应的核上产生中断。第(2)步已经获得了相应的SRIO的端口号,通过SRIO端口号为0或1决定DOORBELLn_ICRR为DOORBELL0_ICRR或DOORBELL1_ICRR。该DOORBELL0_ICRR和DOORBELL1_ICRR分别对应着接收端DSP相应核上的两个SRIO_INT中断。在2.1.3节中已经介绍,借此来判断发送端的DSP的编号。由此接收端能判断出数据在共享调度内存中的存储位置,如图9所示。以发送端为DSP0_Core0、接收端为DSP1_Core1为例,其消息应存储在DSP1的共享内存中的DSP0、Core1段。

(6)接收端DSP相应的核读取共享调度内存的数据,解析收到的消息并通过Mailbox(邮箱)模块,在接收端DSP相应的核内进行核内线程调度,触发相应的任务。

(7)接收端DSP执行完相应的任务后,给发送端返回相应的数据,发送端DSP和Core的编号都会在传输的过程中保存,所以接收端往发送端返回消息时按照前几个步骤的逆过程进行数据传输。

通过以上几个步骤后,多核DSP间的数据传输已经实现。

3数据传输测试

本文对多核DSP间的数据传输进行测试[7],SRIO口的工作速率设置为3.125 Gb/s,经过物理层8B/10B编码,数据包实际传输速率为2.5 Gb/s,使用两个1x通道,理论传输数据为5 Gb/s。

数据传输正确性的测试:从DSP0Core0发送2k次的数据给DSP1Core2,DSP1Core2收到数据后将数据转发给DSP2Core1,DSP2Core1收到数据后再发送回DSP0Core0,DSP0Core0最后将收到的数据与最初发送的数据进行对比,检测数据有无错误。本文采用每隔1 s发送一次数据,测试一星期未发现出错。

传输性能的测试:任意选取两片DSP的任意核进行不同数据长度的回环测试。例如数据从DSP1发送至DSP2,DSP2收到数据后将数据返回给DSP1。从DSP1刚开始发送数据和刚接收完数据后分别利用_itoll(TSCH,TSCL)函数获取CPU的Cycle值,计算两次值之差,即可测出速率[8]。

通过数据分析可以得出,数据的传输速率为2.520 Gb/s左右,为理论值的50.4%。但传输长度为64 B时,传输的数据较少,可近似为线程调度和DSP间同步所需的时间,若将传输32 000 B的时间减去传输64 B时间(线程调度和DSP间同步所需时间),再计算传输速率的值为3.886 Gb/s,为理论值的77.72%。由于数据包的组包和解包,以及DDR上读取数据的开销等,实际数据会小于理论值。

4结束语

本文在DSP_BIOS操作平台上,基于Rapid IO协议,实现了多核DSP间的数据传输。此次设计不仅适用于2个多核DSP间的数据传输,同时也适用于3个甚至3个以上多核DSP间的数据传输。该架构能协同多个DSP进行大量的数据处理,相对减少了单个DSP处理的时延和负担,提高了系统的处理能力和响应速度,对数字信号处理系统的发展具有一定的推动作用。

参考文献

[1] Texas Instruments Group. TMS320 DSP/BIOS v5.42 User’s Guide (SPRU4231) [EB/OL].(2013-08-xx)[2016-09-20]http://www.ti.com.

[2] Texas Instruments Group. TMS320C6474 DSP Semaphore User’s Guide (SPRUG14)[EB/OL].(2016-09-20)[200810xx]http://www.ti.com.

[3] 陈婷,岳强,汪洋.FPGA和DSP间基于SRIO的高速通信系统设计[J].单片机与嵌入式系统应用,2016(3):37-40.

[4] Texas Instruments Group. TMS320C6474 DSP Serial Rapid IO(SRIO) User’s Guide (SPRUG230) [EB/OL].(2011-10-xx)[20160920]http://www.ti.com.

[5] 王磊,王辉球.基于高速串行总线SRIO的数据传输[J].电子制作,2015(5):16-18.

[6] 黄克武,吴海洲.基于TMS320C6455的高速SRIO接口设计[J].电子测量技术,2008,31(9) :143147.

[7] 冯超,张涛.TMS320C6678高速串行接口的传输性能研究[J].单片机与嵌入式系统应用,2015,15(11):52-55.

[8] 侯普.基于TI KeyStoneⅡ多核DSP技术的研究与运用LTEA基带板处理板设计与实现[D].北京:北京邮电大学,2015.

,免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com